Den i särklass mest använda typen av halvledarminne, DRAM, uppfinns 1966 av Robert Dennard. En kondensator och en enda transistor per bit behövs nu, och utveckligen tar fart. Dennard registrerar sitt patent 1968 och 1970 är det dags för Intel att lansera sin första produkt av detta slag, Intel 1103 Dynamic Random Access Memory. Redan 1968 hade Intel börjat sälja 3101, ett 64-bitars SRAM-chip byggt på TTL-teknik, och ett chip med en kapacitet på hela 256 bitar skulle följa kort efter. Jag ber er notera att vi inte talar om bussbredd utan faktiskt lagringskapacitet. Intels första halvledarminne rymde 8 Byte, det senare 32 Byte. Dessa var SRAM-minne, Static RAM, där varje bit lagrades i en bistabil vippa. Informationen i ett sådant är beständig och accesstiden kort. Baksidan är dock att minnet kräver 6 transistorer per byte, mot 1 för DRAM. 256 byte minne kräver alltså 1536 transistorer utöver adressering och busslogik. Detta kan jämföras med de 2300 transistorer som 1970 utgjorde Intels första processor, 4004. Linjebredden i den tidens processer låg runt 10 000 nm, jämfört med dagens 90-130. Denna längskalningsfaktor på ca 100 ger oss 10 000 gånger fler transistorer på samma yta. Storleken på de "wafers" som komponenterna tillverkas på nådde 1970 2,25 tum, ca 57 mm, att jämföra med dagens 300 mm. Trots SRAMs överlägsna prestanda har kostnaden gjort att det för alltid placerats i en nisch, och olika varianter av en-transistor-DRAM utgjort den stora massan av allt minne efter 1980. Nedan visas ett öppet Intel 1103-chip. Korset är rad- och kolonnadresseringslogiken.

Även om 1T-DRAM föregåtts av 3T, med 3 transistorer per bit, är det 1T-DRAM som är är mest intressant. Själva informationen lagras i en kondensator, och både läsning och skrivning sker genom samma transistor. Minnet har mycket stora likheter med kärnminnet. Transistorn adresseras på samma sätt, minnet tillverkas i moduler, där varje modul innehåller en bit från varje ord. Dessa modular packas sedan samman i ett godtyckligt antal kapslar som sedan monteras på kretskort. Kondensatorn i DRAM är såpass liten att den laddas ur på något tiotal mikrosekunder, och måste laddas upp igen med jämna mellanrum. Ca 10% av tiden går åt till denna återskrivning. En bit skrivs genom att transistorn öppnas, och värdet som skall skrivas ligger på kollektorn. Läsning är, liksom i kärnminnet, lite knepigare. Laddningen i kondensatorn är så liten att den förbrukas vid läsning. Därför måste biten återskrivas efter varje läsning, en av orsakerna till att DRAM är långsammare än SRAM. En annan orsak är att även adresseringsledningarna behöver tid att laddas upp och ur. Detta kallas precharge, och sker före varje rad- respektive kolonnadressering. Innan denna är färdig efter en operation kan ingen ny genomföras.

De tidigaste formerna av DRAM innebär att ett ord i taget adresserades genom att man först adresserade raden, sedan kolonnen, där rätt bit fanns. Alla bitar i ett minnesord adresseras parallellt. Varje gång ett nytt ord ska adresseras måste båda adressignalerna skickas på nytt. Då minne ofta läses och skrives sekventiellt fann man snart en bot på detta problem. Lösningen heter Fast Page Mode DRAM och innebär att en rad bara behöver adresseras en gång tills tiden gått ut. Varje ny läsning innebär alltså bara en kolonnadressering, Column Address Strobe. Fyra läsningar hinner göras, vilket sparar in radadressering och väntetider (Row Adress Strobe och precharge) tre gånger av fyra. Hur många operationer som krävdes för en hel läsoperation bestämdes av minnets burst mode, ibland kallat timing. Det är dock inte tal om riktigt samma begrepp som vi är vana vid. Non-FPM DRAM har timings 5-5-5-5 oavsett accesstid eller busshastighet. Det som avses är antalet operationer som krävs för varje läsning, i grupper om fyra. Utan FPM krävs en ny radadressering med tillhörande fördröjningar för varje läsning. Med FPM DRAM använder burst mode 5-3-3-3 eftersom de tre läsningar som följer på den första inte behöver ny radadressering om de ligger på samma rad. Två operationer sparas, RAS och RAS precharge. Hur mycket detta påverkar prestanda beror dels på de olika tiderna som behövs för varje operation, dels i hur stor utsträckning minnet läses sekventiellt. Burst mode mäter antalet operationer, inte tiden det tar att genomföra dem.

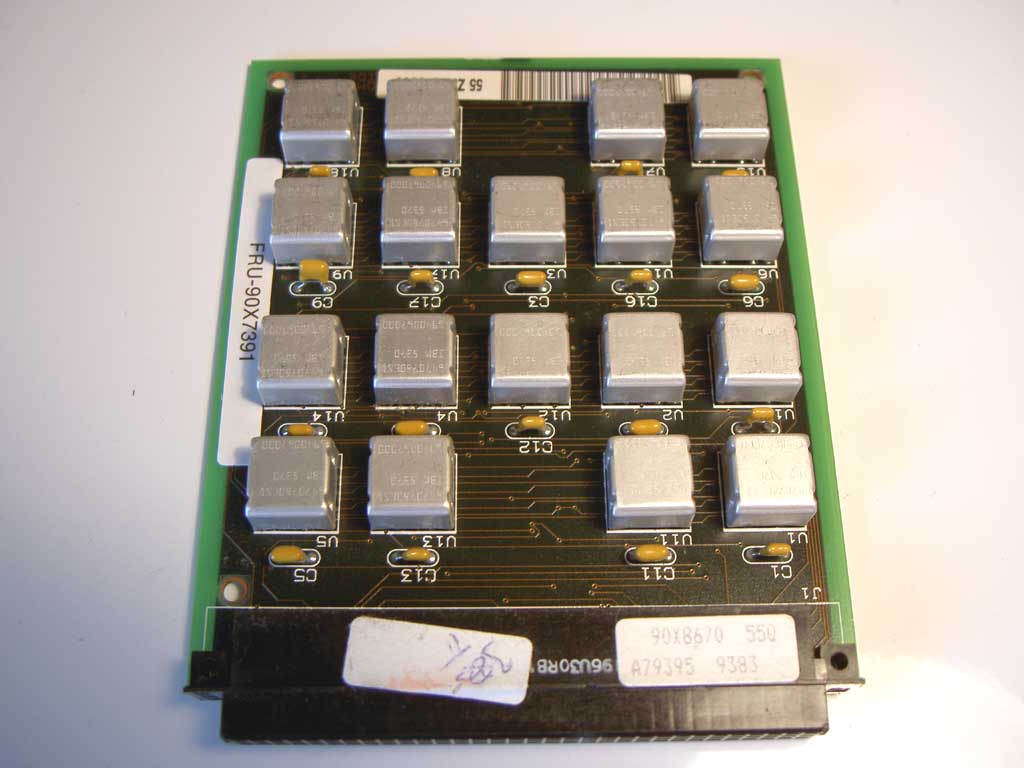

Ovan en 30-pins DRAM-modul.

Denna typ av minne är den första som nådde persondatormarknaden i större mängd. I äldre system monterades det direkt på moderkortet medan man runt mitten av 1980-talet allt oftare monterade socklar för minne. Intel 80386 och 80486 använde 30-pins Single Inline Memory Module, SIMM som format på sina moduler. Bussbredden är då 8 bitar. Då bitfel var relativt vanliga på den tiden använde oftast paritetsminnen, dvs moduler med extra chip, paritetschip. paritetschipet lagrade en paritetsbit för varje byte. Paritetsbiten är en nolla om antalet ettor i en byte är jämnt, en etta om det är udda. Utan paritet har en modul 2, 4, 8, 16 eller 32 chip, där 8 och 16 är vanligast. 32 tar för mycket plats för att rymmas på en 30-pinsmodul, men används flitigt på större modulformat. 2 och 4 moduler används där det är mycket ont om plats, och kräver chip med stor kapacitet. Typiskt används de enbart i laptops och platta rackservrar. Värt att notera är att detta enbart än en fråga om förpacking, innehållet är detsamma, oavsett om det ligger i 2 eller 32 separata chip. Det finns också minnen med andra chipantal, nedan en 72-pins SIMM-modul med 2x12 chip, totalt 2 MB.

Eftersom adressignalerna skickas till alla chip samtidigt går det åt en mycket kraftig ström för att sätta en signalledning till en etta eller nolla. I en vanlig PC stöds maximalt fyra bankar, vanligtvis med 8 chip på varje. Varje adressledare måste då driva 32 ingångar. Att klara av att ändra signalnivå på kort tid med en så stor last är mycket svårt och risken är stor att signalen inte hinner stabiliseras i tid. Detta är orsaken till att det är lättare att överklocka en dator med få bankar än en som är fullsatt. Värre är dock problemen i större datorer, där man ofta har betydligt fler än 4 bankar. Med t ex 32 bankar om vardera 8 chip måste 256 ingångar styras från en utgång i chipset, något som är praktiskt ogenmförbart. För att kringgå detta problem används registrerat, eller buffrat, minne. Istället för att varje chip direktadresseras från chipset buffras signalen i ett register på varje modul. Under påföljande klockcykel adresseras sedan modulens chip av dess egen logik. Minneskontrollern behöver därmed bara driva en ingång per bank istället för en per chip, och kan arbeta mycket snabbare. Priset är en extra klockcykel vid varje adressering.

Paritetsminnena, från början de allra vanligaste, har 1-4 extra chip, 3, 6, 9, 18 eller 36 chip. I takt med att minnesfel blev sällsynta övergavs paritetsminnen, men stödet finns kvar i stor utsträckning. För att ersätta paritet i de system som krävde feltolerans introducerades ECC, Error Correction Code, felrättande kod. Nu kan felen inte bara upptäckas utan även korrigeras. En uppsjö av olika sorters kompatibilitet mellan ECC och paritet finns, vissa ECC-system kan använda paritetsminnen, men det omvända är inte möjligt. En extra komplikation är att inte alla paritetsminnen som tillverkades verkligen lagrade paritet. Istället beräknades paritetsbiten vid läsning, och minneskontrollern fick den paritet den ville ha istället för den äkta. Datorn märker ingen skillnad förrän ett fel inträffar. Som en sista grädde på moset förekom både sk jämn och udda paritet, dvs paritetsbiten kunde inverteras. Vissa datorer krävde en viss sorts paritet, andra hanterade båda sorterna. Under början av 90-talet började 72-pins SIMM-moduler användas i persondatorer. Den viktigaste skillnaden var bandbredden, 32 bitar, som dock stog sig ganska slätt mot de flerkanalsbussar på 128-512 bitar som användes av t ex SUN som monterade 200-pinsmoduler med upp till 40 chip. Idag har man dock gått ifrån 128-bitarsmoduler som den nedan.

Upp till 8 kanaler kunde användas i arbetsstation, samtidigt som PC-datorerna började använda EDO DRAM, som installerades i par, med liknande effekt. EDO står för Extended Data Output och innebär att man inte behöver vänta på att data skickats färdigt innan nästa ord kan adresseras. Data kan då skickas parallellt med kommandon vilket ökar prestanda med 10-20%. Burst mode för EDO DRAM är 5-2-2-2, då en operation kan genomföras parallellt med datatransporten. EDO-minnen gjorde sitt intåg på PC-marknaden 1995 och användes tillsammans med sk Pipeline Burst cache, PB-cache, som innebär en synkronisering mellan cache-minnet och processorns pipeline. EDO-minnen var delvis kompatibla med vanlig DRAM i 72-pins SIMM-kapslar. Vissa moderkort kunde använda båda sorterna tillsammas, men då som om de vore vanlig DRAM.